- 非IC关键词

深圳市华之电科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳保证金额:10000企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳保证金额:10000企业网站:

http://hzd-ic.hqew.com/

收藏本公司 人气:613073

企业档案

- 相关证件:

- 会员类型:

- 会员年限:14年

- 阿库IM:

- 地址:深圳市福田区振华路飞亚达大厦西座925-926室

- E-mail:3005133872@qq.com

相关产品

产品信息

74HCT138D

74HCT138D

74HCT138D

74HCT138D

General description

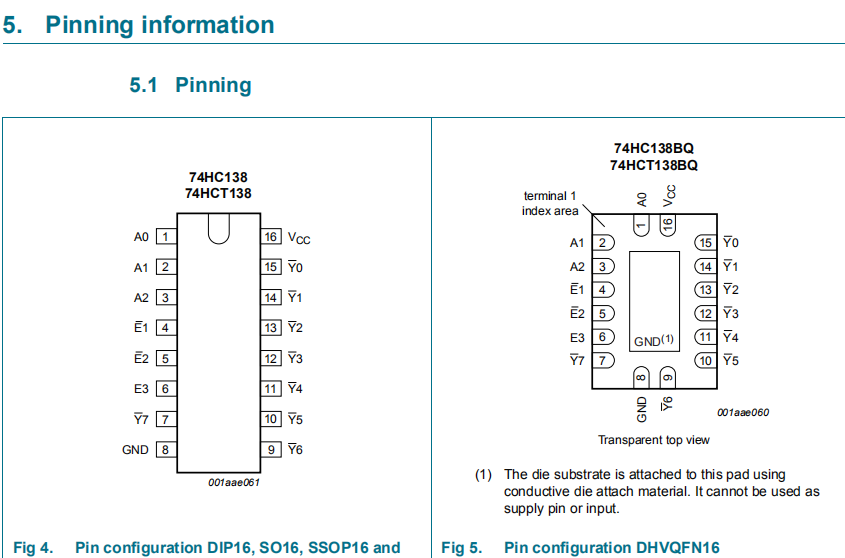

The 74HC138; 74HCT138 is a high-speed Si-gate CMOS device and is pin compatible

with Low-power Schottky TTL (LSTTL).

The 74HC138; 74HCT138 decoder accepts three binary weighted address inputs (A0, A1

and A3) and when enabled, provides 8 mutually exclusive active LOW outputs (Y0 to Y7).

The 74HC138; 74HCT138 features three enable inputs: two active LOW (E1 and E2) and

one active HIGH (E3). Every output is HIGH unless E1 and E2 are LOW and E3 is HIGH.

This multiple enable function allows easy parallel expansion of the 74HC138; 74HCT138

to a 1-of-32 (5 lines to 32 lines) decoder with just four 74HC138; 74HCT138 ICs and one

inverter.

The 74HC138; 74HCT138 can be used as an eight output demultiplexer by using one of

the active LOW enable inputs as the data input and the remaining enable inputs as

strobes. Permanently tie unused enable inputs to their appropriate active HIGH- or

LOW-state.

The 74HC138; 74HCT138 is identical to the 74HC238; 74HCT238 but has inverting

outputs.

2. Features and benefits

Demultiplexing capability

Multiple input enable for easy expansion

Complies with JEDEC standard no. 7A

Ideal for memory chip select decoding

Active LOW mutually exclusive outputs

ESD protection:

HBM EIA/JESD22-A114F exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

Multiple package options

Specified from −40 °C to +85 °C and from −40 °C to +125 °C

询价

询价