- 非IC关键词

深圳市华之电科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳保证金额:10000企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳保证金额:10000企业网站:

http://hzd-ic.hqew.com/

收藏本公司 人气:613690

企业档案

- 相关证件:

- 会员类型:

- 会员年限:14年

- 阿库IM:

- 地址:深圳市福田区振华路飞亚达大厦西座925-926室

- E-mail:3005133872@qq.com

相关产品

产品信息

74HC165D

FEATURES

• Asynchronous 8-bit parallel load

• Synchronous serial input

• Output capability: standard

• ICC category: MSI

74HC165D

GENERAL DESCRIPTION

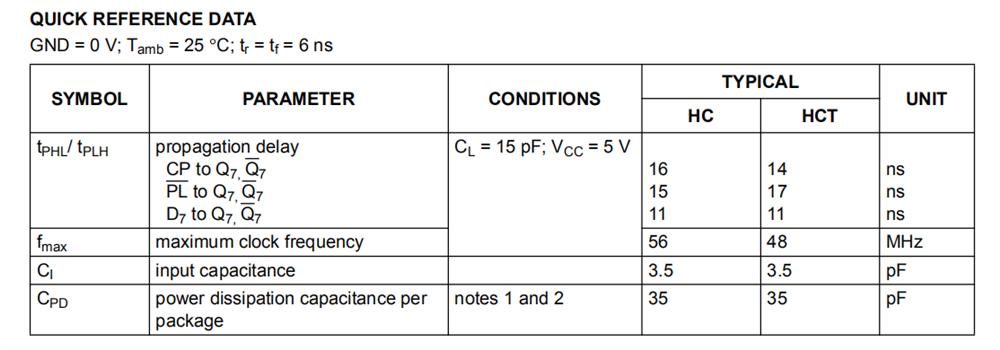

The 74HC/HCT165 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT165 are 8-bit parallel-load or serial-in shift

registers with complementary serial outputs (Q7 and

Q7) available from the last stage. When the parallel load

(PL) input is LOW, parallel data from the D0 to

D7 inputs are loaded into the register asynchronously.

When PL is HIGH, data enters the register serially at the

Ds input and shifts one place to the right

(Q0 → Q1 → Q2, etc.) with each positive-going clock

transition. This feature allows parallel-to-serial converter

expansion by tying the Q7 output to the DS input of the

succeeding stage.

The clock input is a gated-OR structure which allows one

input to be used as an active LOW clock enable (CE) input.

The pin assignment for the CP and CE inputs is arbitrary

and can be reversed for layout convenience. The

LOW-to-HIGH transition of input CE should only take

place while CP HIGH for predictable operation. Either the

CP or the CE should be HIGH before the

LOW-to-HIGH transition of PL to prevent shifting the data

when PL is activated.

74HC165D

APPLICATIONS

• Parallel-to-serial data conversion

74HC165D

74HC165D

询价

询价